What is it about?

This research in high-level synthesis (HLS) focuses on optimizing loop performance through the utilization of modulo scheduling. Modulo scheduling involves interleaving consecutive loop iterations to minimize the initiation interval (II), which represents the number of clock cycles between data insertions within a circuit. Our SAT-based algorithm efficiently computes the optimal II using a problem reduction technique within the framework of iterative modulo scheduling. Subsequently, it conducts an iterative search for the optimal schedule length, leveraging the scalability of modern SAT solvers. This hybrid approach combines the advantages of a heuristic in swiftly determining a feasible solution with the benefits of an exact algorithm in finding the optimal solution given sufficient computation time. Consequently, it can generate implementations for a wide range of practical benchmark applications.

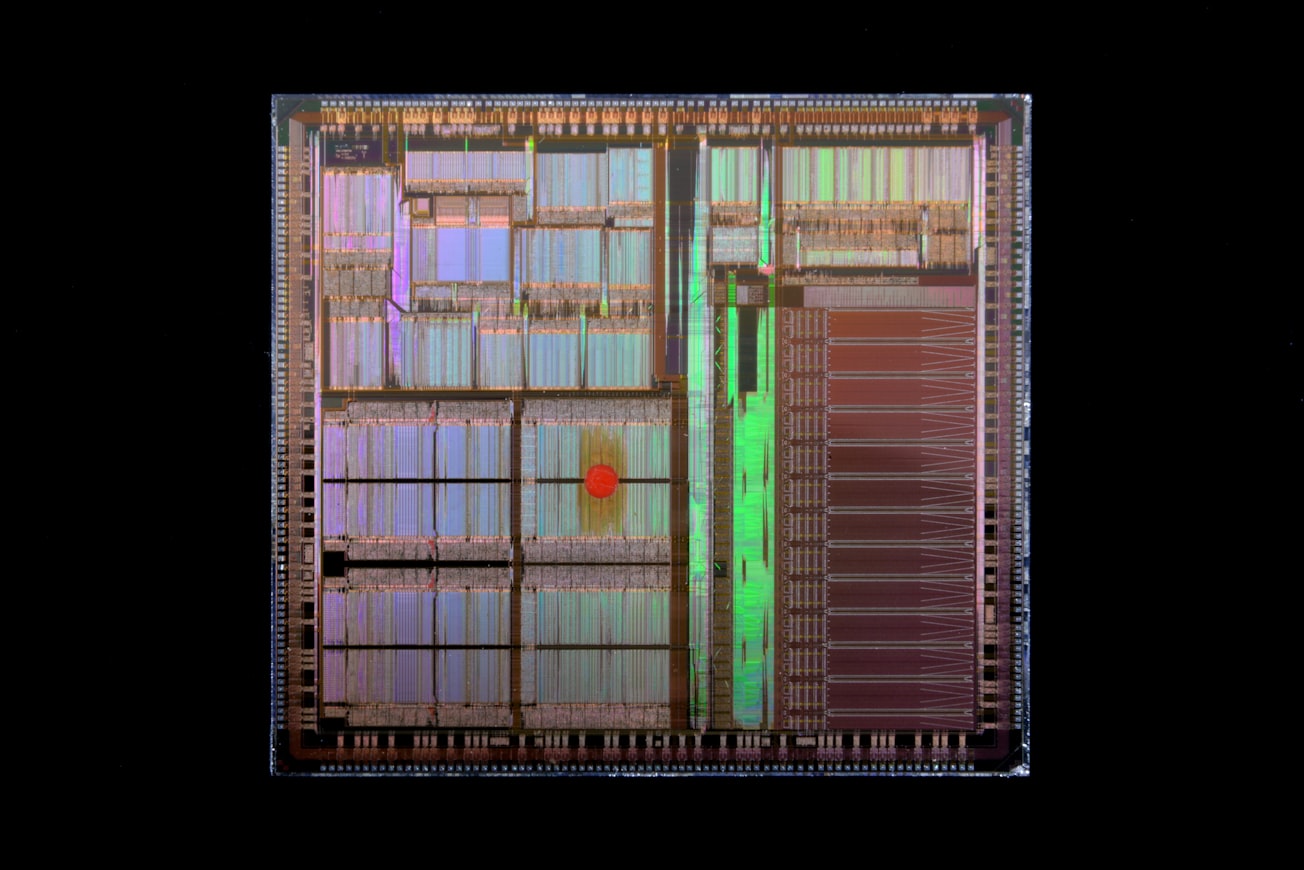

Featured Image

Photo by Laura Ockel on Unsplash

Why is it important?

The design of application-specific hardware implementations is a challenging task when done manually. To automate this process, the extensive employment of HLS algorithms has become crucial. Considering that loop computations often constitute a significant portion of various applications, further accelerating their execution emerges as an imperative pursuit. Many present-day systems, a.o. for image and video processing, machine learning, control engineering, and cryptography, are implemented on field-programmable gate arrays (FPGAs). However, FPGAs demand highly optimized user circuits due to their inherent limitations on speed, area resources, and power efficiency. Our approach surpasses existing solutions in terms of the number of optimally proven solutions and algorithm runtime.

Perspectives

It is truly amazing to witness that, even after decades of intense research on this topic, there still exists a significant opportunity for further contributions and active participation in its ongoing development. Recently, the demand for application-specific hardware architectures has significantly increased, and I firmly believe that advances in the automated construction of such architectures are of paramount interest.

Dr. Peter Zipf

University of Kassel

Read the Original

This page is a summary of: BLOOP: Boolean Satisifiability-based Optimized Loop Pipelining, ACM Transactions on Reconfigurable Technology and Systems, May 2023, ACM (Association for Computing Machinery),

DOI: 10.1145/3599972.

You can read the full text:

Contributors

The following have contributed to this page